# 目 录

| 1. | 产品概述            | 2  |

|----|-----------------|----|

| 2. | 主要特性            | 2  |

| 3. | 系统框图            | 4  |

| 4. | 管脚配置            | 5  |

| 5. | 中央处理器           | 8  |

|    | 5.1 指令集         | 8  |

|    | 5.2 ROM         | 10 |

|    | 5.3 RAM         | 10 |

|    | 5.4 CPU SFR     | 12 |

|    | 5.5 SFR         | 15 |

|    | 5.6 OPTION配置选项  | 17 |

| 6. | 功能模块            | 19 |

|    | 6.1 CLOCK       | 19 |

|    | 6.2 工作模式        | 20 |

|    | 6.3 INT         | 21 |

|    | 6.3.1 中断功能      | 21 |

|    | 6.3.2 中断寄存器     | 21 |

|    | 6.4 GPIO        |    |

|    | 6.5 TIMER       | 30 |

|    | 6.5.1 TIMER0    | 30 |

|    | 6.5.2 TIMER1    |    |

|    | 6.6 LVD         | 39 |

|    | 6.7 TOUCH       |    |

|    | 6.8 ADC         | 41 |

|    | 6.9 WDT         | 45 |

|    | 6.10复位方式        | 46 |

| 7. | 电气特性            | 47 |

|    | 7.1 电气特性极限参数    | 47 |

|    | 7.2 直流特性        | 47 |

|    | 7.3 振荡器特性       | 48 |

|    | 7.4 ADC特性       | 48 |

| 8. | 封装尺寸            | 49 |

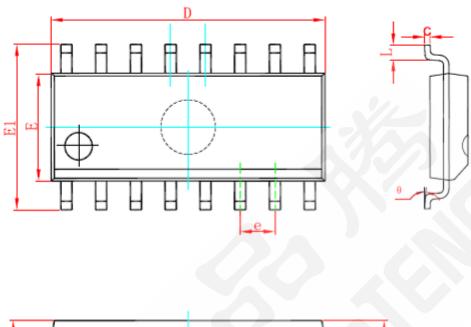

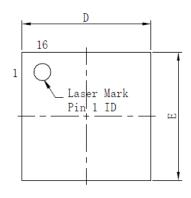

|    | 8.1 SOP16封装     | 49 |

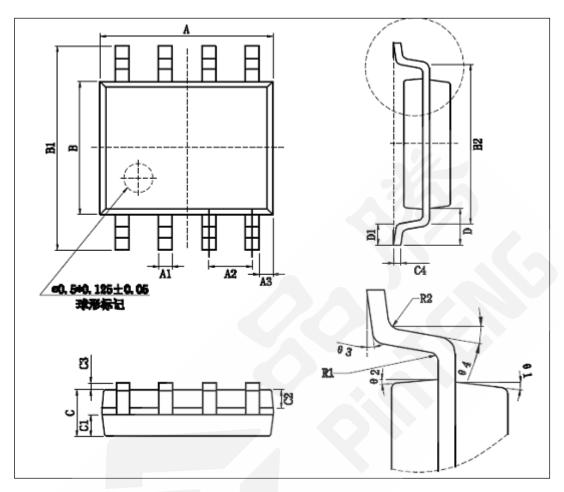

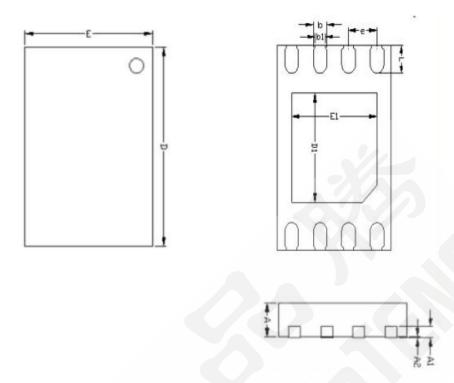

|    | 8.2 SOP8封装      | 50 |

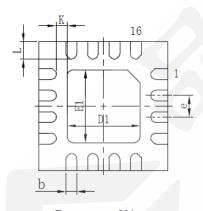

|    | 8.3 QFN16封装     | 51 |

|    | 8.4 DFN2*3-8L封装 | 52 |

| ^  | 压力力量            | 50 |

# 触控 A/D 型 8-Bit MCU

# 1. 产品概述

PT8M2302 是一款可多次编程(MTP)A/D型 8 位 MCU,其包括 2K\*16bit MTP ROM、256\*8bit SRAM、ADC、PWM、Touch 等功能,具有高性能精简指令集、低工作电压、低功耗特性且完全集成触控按键功能。为各种触控按键的应用,提供了一种简单而又有效的实现方法。广泛应用于触摸台灯、小家电、消费类电子产品等电子应用领域。

### 2. 主要特性

#### ■ CPU

- RISC 内核, 支持 66 条指令

- 支持8级硬件堆栈

- 指令周期可配置为 2T/4T/8T/16T

- 复位向量位于 000H

- 支持 6 种中断源, Timer0、Timer1、INT0、INT1、ADC、TOUCH

- 两级中断优先级可设。高优先级中断向量入口: 018h, 低优先级中断向量入口: 008h

- 支持直接与间接数据寻址方式

- 程序存储器 MTP ROM: 2K\*16bit, 可重复烧写 100 次

- 数据存储器 SRAM: 256\*8bit

#### **■ I/O** □

- 13 个双向 I/O 端口,带 SMIT 输入,可配置为漏极开路、内置上拉电阻及下拉电阻

- P10~P17、P01~P04 可配置为触摸通道

- 1个单向输入端口,复用触摸采样电容端口 CMOD

#### ■ 电容式触摸感应模块

- 12 路外部触摸输入

#### ■ ADC

- 12 位 SAR ADC

- 4 路外部输入通道(ADC0~ADC3), 2 路内部特殊通道(内部 VDD/4、内部 GND)

- 3 种参考电压可选: VDD、外部参考电压 VREF、内部基准电压(2.048V)

- 具备初始失调校准功能

#### ■ 定时器

- Timer0

- 自动装载 8 位定时器, 支持预分频功能

- Timer1

- 自动装载 10 位定时器, 支持预分频功能

- 5路独立的 PWM(PWM0~PWM4)

#### ■ CPU 保护系统及工作模式

- 3 种系统复位方式:

- 上电复位(POR)

- 低压复位(LVR)

- 看门狗(WDT)溢出复位

- 支持3种工作模式

- Normal 模式:正常工作模式

- STOP模式:低功耗模式,CPU停止工作,外设停止工作 唤醒方式:外部中断、输入IO电平变化、WDT溢出

- IDLE 模式:仅 CPU 停止工作,其它外设可以工作 唤醒方式:所有中断、输入 IO 电平变化、WDT 溢出

- 内嵌 LVR 功能,复位阈值可选为: 2.0V、2.2V、2.4V、2.7V、2.9V、3.1V、3.3V、3.6V (误差±1%)

- 内嵌 LVD 功能,检测阈值可选为: 2.3V、2.5V、2.9V、4.3V (误差±1%)

- 内嵌 WDT, 支持预分频功能。4 档 WDT 溢出时间可选: 9ms、18ms、144ms、288ms

#### ■ 时钟系统

- 内部 RC 高频振荡器 8MHz 精度: ±0.5%(typ)

- 内部 RC 低频振荡器 32KHz 精度: ±15%(typ)

#### ■ 工作温度范围

- -40°C ~ +85°C

#### ■ 电压工作范围

- 2.7V~5.5V(ADC 使能)

- 2.4V~5.5V(LDO ON)

- 2.2V~5.5V(LDO OFF)

#### ■ 抗干扰能力

- HBM ESD: 优于 5000V

- 封装形式: SOP8、SOP16、QFN16、DFN2\*3-8L

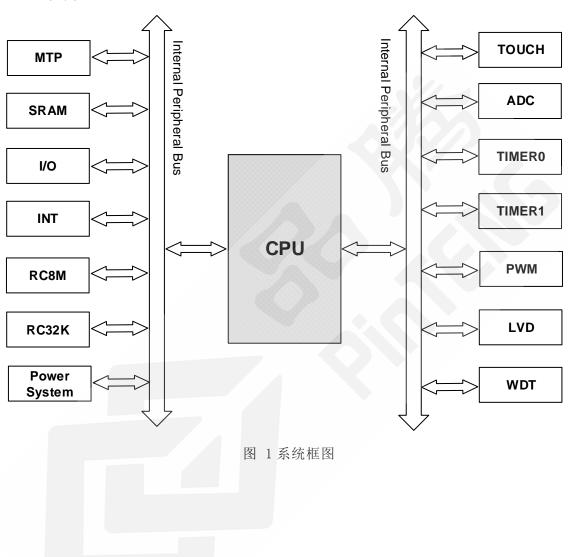

# 3. 系统框图

基于 RISC 的架构绝大部分指令都只需一个指令执行周期,少部分需要两个指令执行周期。内置 2K\*16bit MTP, 256\*8bit SRAM;同时内部集成了 TOUCH、ADC、TIMER、PWM、RC8M、RC32K、WDT、LVD 等外设。

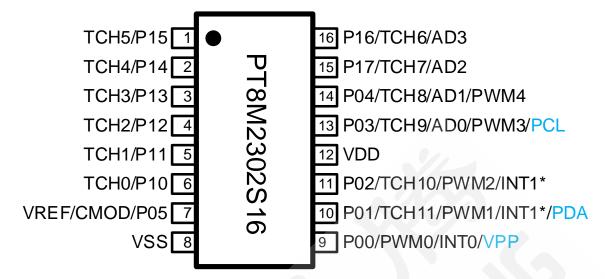

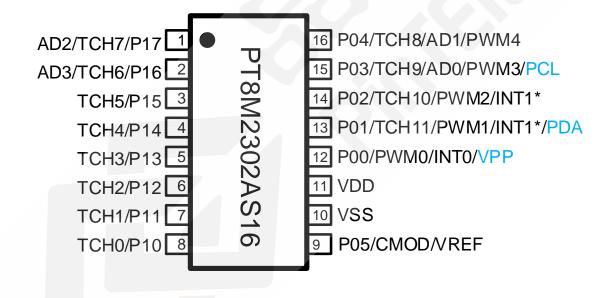

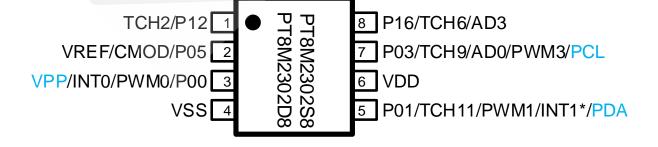

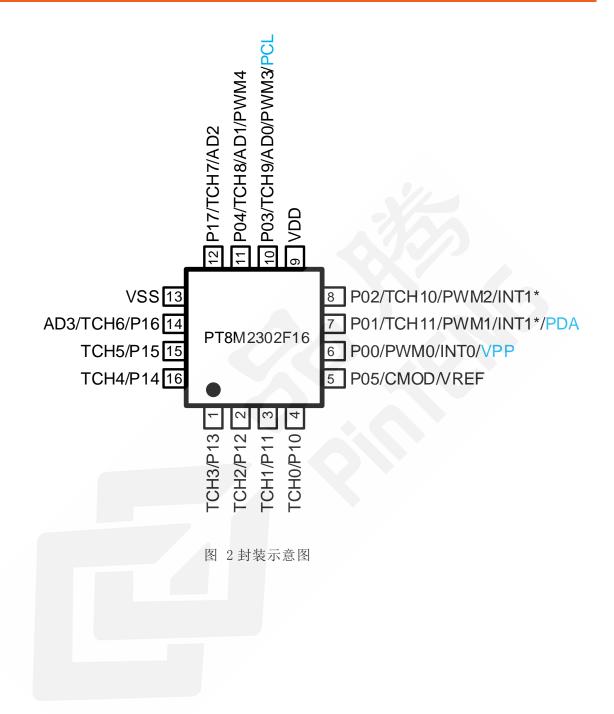

### 4. 管脚配置

# 表 1 管脚信号说明表

| 管脚名称   | I/O类型 | <b>管脚说明</b>                          |

|--------|-------|--------------------------------------|

| VSS    | Р     | 地                                    |

| VDD    | Р     | 电源                                   |

| PWM[i] | 0     | PWM[i]输出口,i=0~4                      |

| TCH[i] | I     | 触摸通道[i],i=0~11                       |

| P0[i]  | I/O   | P0输入/输出IO[i],可配置弱上拉/下拉、开漏输出功能, i=0~5 |

| ı olil |       | (说明: P05只有输入功能)                      |

| P1[i]  | I/O   | P1输入/输出IO[i],可配置弱上拉/下拉、开漏输出功能,i=0~7  |

| VREF   | I     | ADC参考电压输入端口                          |

| AD[i]  | I     | ADC输入通道[i],i=0~3                     |

| INT[i] | I     | 外部中断[i]输入口,i=0~1                     |

| PCL    | I     | 烧录时钟线                                |

| PDA    | İ     | 烧录数据线                                |

| VPP    | Р     | 烧录高压                                 |

注意: \*表示相同功能管脚由 OPTION 配置选项决定。

表 2 管脚信号说明表

| 8M2302S16 | 8M2302AS16 | 8M2302S8 | 8M2302D8 | 8M2302F16 | 管脚名称                    | I/O | 主功能 |       | 兼容功能 |      |      |

|-----------|------------|----------|----------|-----------|-------------------------|-----|-----|-------|------|------|------|

| 1         | 3          | -        | -        | 15        | P15/TCH5                | I/O | P15 | TCH5  |      |      |      |

| 2         | 4          | -        | -        | 16        | P14/TCH4                | I/O | P14 | TCH4  |      |      |      |

| 3         | 5          | 1        | -        | 1         | P13/TCH3                | I/O | P13 | TCH3  |      |      |      |

| 4         | 6          | 1        | 1        | 2         | P12/TCH2                | I/O | P12 | TCH2  |      |      |      |

| 5         | 7          | -        | -        | 3         | P11/TCH1                | I/O | P11 | TCH1  |      |      |      |

| 6         | 8          | -        | -        | 4         | P10/TCH0                | I/O | P10 | TCH0  |      |      |      |

| 7         | 9          | 2        | 2        | 5         | P05/CMOD/VREF           | I/O | P05 |       | CMOD |      | VREF |

| 8         | 10         | 4        | 4        | 13        | VSS                     | Р   | VSS |       |      |      |      |

| 9         | 12         | 3        | 3        | 6         | P00/PWM0/INT0/VPP       | I/O | P00 |       | PWM0 | INT0 | VPP  |

| 10        | 13         | 5        | 5        | 7         | P01/TCH11/PWM1/INT1/PDA | I/O | P01 | TCH11 | PWM1 | INT1 | PDA  |

| 11        | 14         | -        | -        | 8         | P02/TCH10/PWM2/INT1     | I/O | P02 | TCH10 | PWM2 | INT1 |      |

| 12        | 11         | 6        | 6        | 9         | VDD                     | Р   | VDD |       |      |      |      |

| 13        | 15         | 7        | 7        | 10        | P03/TCH9/AD0/PWM3 /PCL  | I/O | P03 | TCH9  | PWM3 | AD0  | PCL  |

| 14        | 16         | -        | -        | 11        | P04/TCH8/AD1/PMW4       | I/O | P04 | TCH8  | PMW4 | AD1  |      |

| 15        | 1          | -        | -        | 12        | P17/TCH7/AD2            | I/O | P17 | TCH7  |      | AD2  |      |

| 16        | 2          | 8        | 8        | 14        | P16/TCH6/AD3            | I/O | P16 | TCH6  |      | AD3  |      |

# 5. 中央处理器

# 5.1 指令集

表 3 MCU 指令集

| 类别           | 指令格式       | 指令意义                    | 周期     | 标志位 |

|--------------|------------|-------------------------|--------|-----|

|              | ADD A, K   | A ← A + K               | 1      |     |

|              | ADD A, R   | A ← A + R               | 1      |     |

|              | ADDR A, R  | $R \leftarrow A + R$    | 1      |     |

|              | ADDC A, R  | A ← A + R + C           | 1      | С   |

| 算术运算         | ADDCR A, R | R ← A + R + C           | 1      | DC  |

| 异小色异         | SUB A, K   | A ← A -K                | 1      | Z   |

|              | SUB A, R   | A ← A - R               | 1      | OV  |

|              | SUBR A, R  | R ← A - R               | 1      |     |

|              | SUBC A, R  | A ← A - R - (~C)        | 1      |     |

|              | SUBCR A, R | R ← A - R - (~C)        | 1      |     |

|              | AND A, K   | A ← A & K               | 1      | Z   |

|              | AND A, R   | A ← A & R               | 1      | Z   |

|              | ANDR A, R  | R ← A & R               | 1      | Z   |

|              | OR A, K    | A ← A   K               | 1      | Z   |

| 逻辑运算         | OR A, R    | A ← A   R               | 1      | Z   |

| <b>心</b> 再色异 | ORR A, R   | $R \leftarrow A \mid R$ | 1      | Z   |

|              | XOR A, K   | A ← A ^ K               | 1      | Z   |

|              | XOR A, R   | A ← A ^ R               | 1      | Z   |

|              | XORR A, R  | R ← A ^ R               | 1      | Z   |

|              | BCPL R, b  | R的第b个位取反,然后送给R          | 1      | ~   |

|              | INC R      | A ←R + 1                | 1      | Z   |

|              | INCR R     | R ←R + 1                | 1      | Z   |

|              | INCSZ R    | A←R+1,如果A=0,则跳过下一条指令    | 1 or 2 | ~   |

| 递增和递         | INCSZRR    | R←R+1,如果R=0,则跳过下一条指令    | 1 or 2 | ~   |

| 减指令          | DEC R      | A ←R - 1                | 1      | Z   |

|              | DECR R     | R ←R - 1                | 1      | Z   |

|              | DECSZ R    | A ←R - 1,如果A=0,则跳过下一条指令 | 1 or 2 | ~   |

|              | DECSZR R   | R ←R - 1,如果R=0,则跳过下一条指令 | 1 or 2 | ~   |

|              | RLC R      | A←R带进位循环左移1位            | 1      | С   |

|              | RLCR R     | R←R带进位循环左移1位            | 1      | С   |

|              | RRC R      | A ← R带进位循环右移1位          | 1      | С   |

| 移位指令         | RRCR R     | R ← R带进位循环右移1位          | 1      | С   |

|              | RL R       | A ← R循环左移1位             | 1      | ~   |

|              | RLR R      | R←R循环左移1位               | 1      | ~   |

|              | RR R       | A ← R循环右移1位             | 1      | ~   |

|                | RRR R      | R ← R循环右移1位                                                                     | 1      | ~  |

|----------------|------------|---------------------------------------------------------------------------------|--------|----|

|                | MOV A, R   | A←R                                                                             | 1      | Z  |

|                | MOV A, R   | R ← A                                                                           |        | ~  |

|                |            |                                                                                 | 1      |    |

|                |            | A←K                                                                             | 1      | ~  |

| *** 1日 (十 ) ** | MOV R, R   | R ← R,两个R为同一地址,影响Z                                                              | 1      | Z  |

| 数据传送           | MOVAR R    | A ← RAM[R], R为11bit值(R为8位)                                                      | 1      | Z  |

|                | MOVRA R    | RAM[R] ← A,R为11bit值(R为8位)                                                       | 1      | ~  |

|                | DPSEL K    | DPAGE ← K                                                                       | 1      | ~  |

|                | MPSEL K    | 13bit的K赋值给MP                                                                    | 2      | ~  |

|                | ESEL K     | 11bit的K赋值给{EADRH,EADRL}                                                         | 2      | ~  |

| 偏移计算           | MSTEP K    | MP←MP + K(-128≤K≤127)                                                           | 1      | ~  |

| PIN 12 VI 31   | ESTEP K    | EADR←EADR + K(-128≤K≤127)                                                       | 1      | ~  |

| 位操作            | BCLR R, b  | R[b] ← 0                                                                        | 1      | ~  |

| 121×11         | BSET R, b  | R[b] ← 1                                                                        | 1      | ~  |

|                | JMP AA     | PC←AA,AA为13bit值,JMP可跳转8K<br>ROM空间                                               | 2      | ~  |

|                | BTSZ R, b  | 如果R[b]=0,则跳过下一条指令                                                               | 1 or 2 | ~  |

|                | BTSNZ R, b | 如果R[b]=1,则跳过下一条指令                                                               | 1 or 2 | ~  |

| 转移指令           | CALL AA    | Push pc+1,then PC←AA,AA为13bit<br>值,CALL可跳转8K ROM空间                              | 2      | ~  |

|                | RET        | PC值出栈                                                                           | 2      | ~  |

|                | RET A, K   | PC值出栈同时K赋给累加器A                                                                  | 2      | ~  |

|                | RETI       | PC值出栈同时全局中断使能置1                                                                 | 2      | ~  |

|                | SE R       | 如果A=R,则跳过下一条指令                                                                  | 1 or 2 | CZ |

|                | SE K       | 如果A=K,则跳过下一条指令                                                                  | 1 or 2 | CZ |

|                | NOP        | 空指令不作任何操作                                                                       | 1      | ~  |

|                | CLR R      | 把RAM(R)中的值赋0                                                                    | 1      | Z  |

|                | CLRWDT     | Clear WDT                                                                       | 1      | ~  |

| 其它指令           | SWAP R     | R的高四位和低四位交换,结果放入A                                                               | 1      | ~  |

|                | SWAPR R    | R的高四位和低四位交换,结果放入R                                                               | 1      | ~  |

|                | STOP       | 芯片进入STOP状态                                                                      | 1      | ~  |

|                | IDLE       | 芯片进入IDLE状态                                                                      | 1      | ~  |

| 查表             | MOVC R     | ROM[EADRH, EADRL]→ [EDATH, R]把<br>ROM地址(EADRH, EADRL)中的值高8位<br>赋给EDATH, 低8位赋值给R | 2      | ~  |

### 参数说明:

R:

数据存储器地址

A:

工作寄存器

k:

立即数

b:

位选择(0~7)

PC:

程序计数器

C:

进位标志

DC: 半加进位标志 Z: 结果为零标志

#### **5.2 ROM**

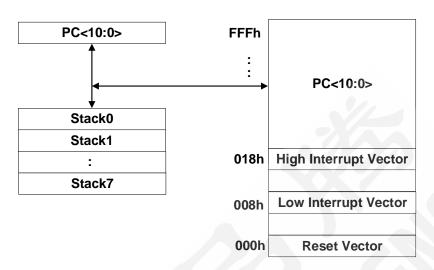

2K×16bit 的存储空间,由 11 位 PC 指针访问,复位地址为 000h,中断向量地址 008h 或 018h,支持 8 级堆栈,程序存储器和堆栈结构如下:

图 3程序存储器 ROM

■ 说明: 堆栈级数为8级,如果用户使用时超过此级数,则会导致功能出错

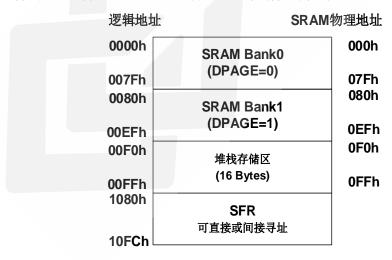

#### **5.3 RAM**

有一个 256×8bit 的数据存储空间(通过 DPAGE 配置为 2 个 Bank),最后 16\*8bit 空间用于堆栈操作指令(软件不可访问)。逻辑地址和 SRAM 物理地址映射关系如下:

图 4 数据存储器 SRAM

数据存储器主要用于程序运行过程中全局以及中间变量的存储。数据存储器一共有 256 个单元(最后 16 字节为堆栈存储空间),它的物理地址可被划分为如下区域:

- 分页 0 数据存储区: 000h~07Fh (DPAGE=0)

- 分页 1 数据存储区: 080h ~ 0EFh (DPAGE=1)

- 堆栈存储区: 0F0h~0FFh

www.pintengtech.com 版本号 V1.4 10 / 53

#### 1. 直接寻址

- 1. 直接寻址地址空间分为低 128 字节和高 128 字节:

- (1) 低 128 字节(R[7:0]< 0x80)为 SRAM 寻址,由{DPAGE,R[6:0]}组成 RAM 物理寻址。

- (2) 高 128 字节(R[7:0]>= 0x80)为 SFR 寻址, SFR 地址与 DPAGE 无关。

- 2. SFR 地址空间可直接寻址,也可间接寻址;

- 3. MOVAR/MOVRA 为 SRAM 物理地址直接寻址指令:

- (1) MOVAR R 指令: R 为 8 位地址空间,将 R[7:0]地址中的值读到 ACC 寄存器;

- (2) MOVRA R 指令: R 为 8 位地址空间,将 ACC 寄存器的值写到 R[7:0]地址中。

#### 2. 间接寻址

间接寻址空间包括所有 SRAM 空间及 SFR 空间。间接寻址地址 MPH0[4]等于 0 时为寻址 SRAM,通过间接寻址地址寄存器 MPL0[7:0]来访问其物理地址;

间接寻址地址 MPH0[4]等于 1 时为寻址 SFR, 间接寻址 SFR 的物理地址为: MPL0[7:0]。 映射关系如下图所示:

#### 说明:

- 1. 间接寻址 SRAM 堆栈存储区时,功能将出错

- 2. 间接寻址 SFR 空间时, 寻址地址为 MPL0[7:0] (MPH0[4]=1)

#### 5.4 CPU SFR

CPU 模块相关寄存器:

| 地址    | 符号     | Bit7  | Bit6                            | Bit5 | Bit4 | Bit3    | Bit2 | Bit1 | Bit0  | 复位值       |  |  |

|-------|--------|-------|---------------------------------|------|------|---------|------|------|-------|-----------|--|--|

| 1080h | IAR0   | 通过{MF | 通过{MPH0,MPL0}访问数据区(不是一个实际的物理地址) |      |      |         |      |      |       |           |  |  |

| 1082h | MPL0   |       | MPL0[7:0]                       |      |      |         |      |      |       |           |  |  |

| 1083h | MPH0   |       | MPH0[7:0]                       |      |      |         |      |      |       |           |  |  |

| 1086h | STATUS | SPDF  | -                               | -    | -    | -       | Z    | DC   | С     | 0xxx      |  |  |

| 1087h | ACC    |       |                                 |      | ACC  | [7:0]   |      |      |       | xxxx xxxx |  |  |

| 1088h | PCL    |       |                                 |      | PCL  | [7:0]   |      |      |       | 0000 0000 |  |  |

| 1089h | DPAGE  | -     | -                               | -    | -    | -       | -    | 1-7  | DPAGE | 0         |  |  |

| 10F2h | EADRH  |       |                                 |      | EADF | RH[7:0] |      |      |       | XXXX XXXX |  |  |

| 10F3h | EADRL  |       | EADRL[7:0]                      |      |      |         |      |      |       |           |  |  |

| 10F4h | EDATH  |       |                                 |      | EDAT | H[7:0]  |      |      |       | XXXX XXXX |  |  |

#### ● 间接寻址寄存器(IAR0, MPH0,MPL0):

IARO 不是一个实际的物理地址。当间接寻址地址 MPH0[4]等于 0 时为寻址 SRAM,通过间接寻址地址寄存器 MPL0[7:0]来访问其物理地址;间接寻址地址 MPH0[4]等于 1 时为寻址 SFR,间接寻址 SFR的物理地址为: MPL0[7:0]。MPH0 只能使用直接寻址方式写入。

# • 状态寄存器(STATUS, 1086h):

状态寄存器包含运算标志,结果标志。

| ВІТ     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|------|------|------|------|------|

| Name    | SPDF | -    | -    | -    | -    | Z    | DC   | С    |

| Access  | R    | -    | -    | -    | -    | R/W  | R/W  | R/W  |

| Default | 0    | -    | -    | -    | -    | х    | х    | х    |

Bit[7] SPDF: 加速模式标志

1: 加速模式

0: 无加速模式

上述加速模式是指上电复位时间(18ms)

Bit[2] **Z:** 零标志

1: 算术或逻辑操作结果为 0

0: 算术或逻辑操作结果不为0

Bit[1] DC: 辅助进位标志/借位标志,用于借位时,极性相反

Bit[0] C: 进位标志/借位标志,用于借位时,极性相反

#### • 数据存储器页面选择(DPAGE, 1089h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0  |

|---------|------|------|------|------|------|------|------|-------|

| Name    | -    | -    | -    | -    | -    | -    | -    | DPAGE |

| Access  | -    | -    | -    | -    | -    | -    | -    | R/W   |

| Default | -    | -    | -    | -    | -    | -    | -    | 0     |

DPAGE 只在 SRAM 直接寻址时使用,按如下方式进行分页选择:

| DPAGE | BANK值 | 数据存储器对应逻辑地<br>址 | 数据存储器对应物理地址 |  |

|-------|-------|-----------------|-------------|--|

| 0     | Bank0 | 000h ~ 07Fh     | 000h ~ 07Fh |  |

| 1     | Bank1 | 080h ~ 0EFh     | 080h ~ 0EFh |  |

#### • 累加器(ACC, 1087h):

Accumulator 是一个内部数据转化、指令操作和存放操作结果的存储单元

| BIT     | Bit7               | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |

|---------|--------------------|------|------|------|------|------|------|------|--|

| Name    | ACC<br>R/W<br>0xxx |      |      |      |      |      |      |      |  |

| Access  |                    |      |      |      |      |      |      |      |  |

| Default |                    |      |      |      |      |      |      |      |  |

#### • PC 指针低 8 位(PCL, 1088h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |

|---------|------|------|------|------|------|------|------|------|--|

| Name    |      |      |      | P    | CL   |      |      |      |  |

| Access  |      |      |      | R/W  |      |      |      |      |  |

| Default | 0x00 |      |      |      |      |      |      |      |  |

PCL 只能通过 **ADDR A**, **PCL** 指令跳转(注: 执行此指令后 PC=PC+PCL, PCL=PCL+ACC; 除此指令外,对 PCL 操作的其它指令不能改变 PC 值)。

软件可以读取它得到 PC 的低 8 位的值,比如: "MOV A,PCL"等,对 PCL 的间接寻址也是无效的。

#### MOVC 地址寄存器(EADRH, 10F2h):

| BIT     | Bit7 | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |  |  |

|---------|------|------------|------|------|------|------|------|------|--|--|--|--|

| Name    |      | EADRH[7:0] |      |      |      |      |      |      |  |  |  |  |

| Access  |      | R/W        |      |      |      |      |      |      |  |  |  |  |

| Default |      | xxx        |      |      |      |      |      |      |  |  |  |  |

Bit[7:0] **EADRH[7:0]**: 读取程序存储器的地址高 8 位

#### MOVC 地址寄存器(EADRL, 10F3h):

| BIT     | Bit7 | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|------------|------|------|------|------|------|------|--|--|

| Name    |      | EADRL[7:0] |      |      |      |      |      |      |  |  |

| Access  |      |            |      | R/   | W    |      |      |      |  |  |

| Default |      |            |      | 0x   | xx   |      |      |      |  |  |

Bit[7:0] **EADRL[7:0]**: 读取程序存储器的地址低 8 位

#### MOVC 数据寄存器(EDATH, 10F4h):

| BIT     | Bit7 | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |  |

|---------|------|------------|------|------|------|------|------|------|--|--|--|

| Name    |      | EDATH[7:0] |      |      |      |      |      |      |  |  |  |

| Access  |      |            |      | R/   | W    |      |      |      |  |  |  |

| Default |      |            |      | 0x:  | xx   |      |      |      |  |  |  |

Bit[7:0] **EDATH[7:0]**: 程序存储器数据在 **SFR** 中的存储地址。

ROM[EADRH, EADRL]→[EDATH, R], 即把 ROM 地址[EADRH, EADRL]中的值高 8 位赋给 SFR 的 EDATH, 低 8 位赋值给 SRAM 的 R 地址

举例:将程序存储器地址 0123h 中的数据传送到 SFR 的 EDATH 和 55h,然后再将高 8 位数据赋值给 ACC

MOV A,#0x01

MOV EADRH,A //send ROM Hbyte address to EADRH

MOV A,#0x23

MOV EADRL, A //send ROM Lbyte address to EADRL

MOVC 0x55

MOV A, EDATH //send Hbyte data to ACC

### 5.5 SFR

特殊功能寄存器(SFR)包含系统专用寄存器和辅助专用寄存器,详细描述如下所示: 表 4 寄存器列表 (SFR)

| 地址    | 符号     | Bit7     | Bit6      | Bit5           | Bit4      | Bit3         | Bit2        | Bit1    | Bit0   | 复位值       |

|-------|--------|----------|-----------|----------------|-----------|--------------|-------------|---------|--------|-----------|

| 1080h | IAR0   |          | 通过{M      | PH0,MPL        | 0}访问数据[   | 区(不是一个       | 实际的物        | 理地址)    |        | xxxx xxxx |

| 1082h | MPL0   |          |           |                | MPL0      | [7:0]        |             |         |        | xxxx xxxx |

| 1083h | MPH0   |          |           |                | MPHO      | [7:0]        |             |         |        | xxxx xxxx |

| 1086h | STATUS | SPDF     | -         | -              | -         | -            | Z           | DC      | С      | 0xxx      |

| 1087h | ACC    |          |           |                | ACC       | [7:0]        |             |         |        | xxxx xxxx |

| 1088h | PCL    |          |           |                | PCL[      | 7:0]         |             |         |        | 0000 0000 |

| 1089h | DPAGE  | -        | 1         | -              | -         | -            | _           | -       | DPAGE  | 0         |

| 108Bh | IE0    | GIE/GIEL | GIEH      | 1              | INT1IE    | INT0IE       | -           | T1IE    | TOIE   | 00-0 0-00 |

| 108Ch | IF0    | -        | 1         | -              | INT1IF    | INT0IF       | -           | T1IF    | T0IF   | 0 0-00    |

| 108Dh | IE1    | -        | -         | -              |           | _            | -           | ADCIE   | THIE   | 00        |

| 108Eh | IF1    | -        | -         | -              | -         | -            | -           | ADCIF   | THIF   | 00        |

| 1091h | IP0    | IPEN     | -         | -              | INT1IP    | INT0IP       | -           | T1IP    | T0IP   | 00 0-00   |

| 1092h | IP1    | -        | -         | -              | _         | - (          | -           | ADCIP   | THIP   | 00        |

| 1094h | INTS   | -        | -         | -              |           | INT18        | S[1:0]      | INT0    | S[1:0] | 0000      |

| 1095h | INTEN  | -        | -         | -              | EINT[1:0] |              |             |         |        | 00        |

| 1096h | WDTCON | LRCEN    | WDTSEL    | WDTEN          | ТО        | PD           |             | PS[2:0] |        | 1011 1111 |

| 1098h | BDGC   |          |           |                | BDGC      | [7:0]        |             |         |        | xxxx xxxx |

| 1099h | P0     | -        | -         |                |           | P0[5         | :0]         |         |        | xx xxxx   |

| 109Ah | P0OD   | -        | -         | -              |           | P            | 0OD[4:0]    |         |        | 0 0000    |

| 109Bh | P0PH   | -        | -         |                |           | P0PH[        | 5:0]        |         |        | 11 1111   |

| 109Ch | P0PD   | -        | -         |                |           | P0PD[        | 5:0]        |         |        | 00 0000   |

| 109Dh | P00E   | _        | _         | -              |           | P            | 00E[4:0]    |         |        | 1 1111    |

| 109Fh | P0WK   | -        | 1         |                |           | P0WK[        | [5:0]       |         |        | 00 0000   |

| 10A0h | P1     |          |           |                | P1[7      | <b>7</b> :0] |             |         |        | xxxx xxxx |

| 10A1h | P1OD   |          |           |                | P10D      | [7:0]        |             |         |        | 0000 0000 |

| 10A2h | P1PH   |          |           |                | P1PH      | [7:0]        |             |         |        | 1111 1111 |

| 10A3h | P1PD   |          | P1PD[7:0] |                |           |              |             |         |        | 0000 0000 |

| 10A4h | P10E   |          | P10E[7:0] |                |           |              |             |         |        |           |

| 10A6h | P1WK   |          |           | P1WK[7:0]      |           |              |             |         |        |           |

| 10B6h | T0CON0 | -        | -         | T0FS[2:0] T0EN |           |              |             |         |        |           |

| 10B9h | T0C    |          |           |                | T0C[      | 7:0]         |             |         |        | 0000 0000 |

| 10BAh | T00VR  |          |           |                | TOOVE     | R[7:0]       | <del></del> |         |        | xxxx xxxx |

# PT8M2302 规格书

| 10BDh | T1CON0 | -     | _             | -      | -       |        | T1FS[2:0] |         | T1EN      | 0000      |  |  |

|-------|--------|-------|---------------|--------|---------|--------|-----------|---------|-----------|-----------|--|--|

| 10BEh | T1CON1 | -     | -             | -      | PWM4EN  | PWM3EN | PWM2EN    | PWM1EN  | PWM0EN    | 0 0000    |  |  |

| 10BFh | T1CON2 | -     | -             | -      | PWM4S   | PWM3S  | PWM2S     | PWM1S   | PWM0S     | 0 0000    |  |  |

| 10C0h | T10VRL |       |               |        | T10VR   | L[7:0] |           |         |           | xxxx xxxx |  |  |

| 10C1h | T10VRH |       | - T10VRH[1:0] |        |         |        |           |         |           |           |  |  |

| 10C2h | T1CL   |       | T1CL[7:0]     |        |         |        |           |         |           |           |  |  |

| 10C3h | T1CH   |       |               |        | -       |        |           | T1CH    | H[1:0]    | 00        |  |  |

| 10C4h | T1D0L  |       |               |        | T1D0L   | [7:0]  | 2//       |         |           | xxxx xxxx |  |  |

| 10C5h | T1D0H  |       |               |        | -       |        |           | T1D0    | H[1:0]    | xx        |  |  |

| 10C6h | T1D1L  |       |               |        | T1D1L   | [7:0]  |           |         |           | xxxx xxxx |  |  |

| 10C7h | T1D1H  |       | - T1D1H[1:0]  |        |         |        |           |         | xx        |           |  |  |

| 10C8h | T1D2L  |       | T1D2L[7:0]    |        |         |        |           |         | xxxx xxxx |           |  |  |

| 10C9h | T1D2H  |       | - T1D2H[1:0]  |        |         |        |           |         |           | xx        |  |  |

| 10CAh | T1D3L  |       | T1D3L[7:0]    |        |         |        |           |         |           |           |  |  |

| 10CBh | T1D3H  |       |               |        | -       |        |           | T1D3    | H[1:0]    | xx        |  |  |

| 10CCh | T1D4L  |       |               |        | T1D4L   | [7:0]  |           |         |           | xxxx xxxx |  |  |

| 10CDh | T1D4H  |       |               |        | -       | ٠. (   |           | T1D4    | H[1:0]    | xx        |  |  |

| 10DBh | ADCON0 | A     | DCCK[2:0      | 0]     | ADCE    |        | ADCS      | PT[3:0] |           | 0000 0000 |  |  |

| 10DCh | ADCON1 | ADCVO | -             | -      | ADCS    | ADCEN  | AE        | CVREF[2 | 1:0]      | 00 0000   |  |  |

| 10DDh | ADCON2 |       | -             | ADCCUR | ADCCALD |        | ADCC      | AL[3:0] |           | 00 0000   |  |  |

| 10DEh | ADCON3 | _     | _             | -      | -       | -      | AE        | CADDR[2 | 2:0]      | 000       |  |  |

| 10DFh | ADCCH0 | -     | -             | -      | -       |        | ADCC      | H0[3:0] |           | 0000      |  |  |

| 10E3h | ADCOL  |       |               |        | ADCOL   | _[7:0] |           |         |           | 0000 0000 |  |  |

| 10E4h | ADCOH  | -     | _             | -      | -       |        | ADCC      | H[3:0]  |           | 0000      |  |  |

| 10F2h | EADRH  |       |               |        | EADRH   | H[7:0] |           |         |           | xxxx xxxx |  |  |

| 10F3h | EADRL  |       | EADRL[7:0]    |        |         |        |           |         |           |           |  |  |

| 10F4h | EDATH  |       |               |        | EDATH   | I[7:0] |           |         |           | xxxx xxxx |  |  |

| 10F5h | LVDCON | _     | _             |        | -       | LVDOUT | LVDEN     | LVDSI   | EL[1:0]   | 0000      |  |  |

|       |        |       |               |        |         |        |           |         |           |           |  |  |

说明:

- : 无效位,回读为'0'

x : 不定态

# **5.6 OPTION**配置选项

表 5 配置选项 0(7F8h)

| 名称          | 位       | 默认值 | 说明                                             |

|-------------|---------|-----|------------------------------------------------|

|             |         |     | RC8M 时钟及 32K 内部时钟输出使能                          |

| OSC_OUT     | [15]    | 0   | 1: RC8M 时钟通过 P01 输出, RC32K 时钟通过 P02 输出         |

|             |         |     | 0: P02、P01 不输出时钟                               |

|             |         |     | 低电压复位使能位                                       |

| LVREN       | [14]    | 1   | 1: 使能 LVR                                      |

|             |         |     | 0: 关闭 LVR                                      |

|             |         |     | 低电压复位点选择                                       |

|             |         |     | 000: 2.0V                                      |

|             |         |     | 001: 2.2V                                      |

|             |         |     | 010: 2.4V                                      |

| LVRSEL[2:0] | [13:11] | 001 | 011: 2.7V                                      |

|             |         |     | 100: 2.9V                                      |

|             |         |     | 101: 3.1V                                      |

|             |         |     | 110: 3.3V                                      |

|             |         |     | 111: 3.6V                                      |

|             |         |     | PWRT & WDT 计数周期选择位 (其值必须是分频率的倍数)               |

|             |         |     | 11: PWRT = WDT prescaler rate = 18ms (default) |

| SUT[2:0]    | [9:8]   | 11  | 10: PWRT = WDT prescaler rate = 9ms            |

|             |         |     | 01: PWRT = WDT prescaler rate = 288ms          |

|             |         |     | 00: PWRT = WDT prescaler rate = 144ms          |

# 表 6 配置选项 1(7F9h)

| 名称         | 位     | 默认值 | 说明                                    |

|------------|-------|-----|---------------------------------------|

|            |       |     | BANDGAP 修调功能屏蔽位                       |

| BDGC_ID    | [15]  | 1   | 1: BANDGAP 修调功能屏蔽                     |

|            |       |     | 0: BANDGAP 修调功能不屏蔽                    |

|            |       |     | 选择 CMOD 口作为触摸/AD 模拟口或数字输入口            |

| CMODFS     | [13]  | 1   | 0: 作为数字输入口                            |

|            |       |     | 1: 作为触摸/AD 模拟口                        |

|            |       |     | 代码保护选择位                               |

| PROTECT    | [10]  | 1   | 1: 代码不加密 MTP code protection off (默认) |

|            |       |     | 0: 代码加密 MTP code protection on        |

|            |       |     | INT1 输入脚选择位                           |

| INT1SEL    | [9]   | 0   | 1: INT1 从 P02 脚输入                     |

|            |       |     | 0: INT1 从 P01 脚输入                     |

|            |       |     | 指令周期选择位(Instructions Period Select)   |

|            |       |     | = 11: 4T: 4 个 RC8M 周期 (默认)            |

| IPSEL[1:0] | [3:2] | 11  | = 10: 2T : 2 个 RC8M 周期                |

|            |       |     | = 00: 8T : 8 个 RC8M 周期                |

|            |       |     | = 01: 16T: 16 个 RC8M 周期               |

# 6. 功能模块

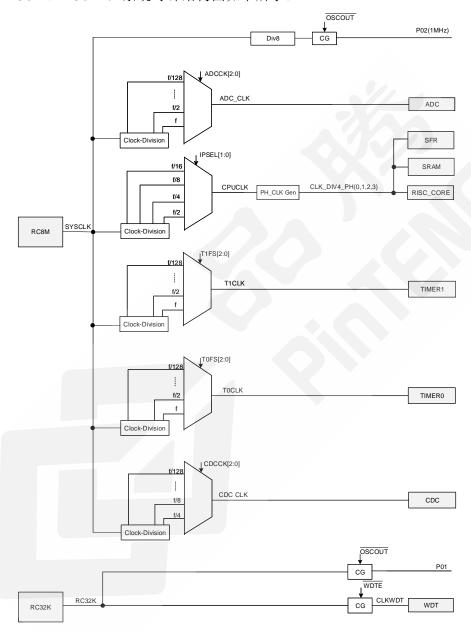

#### 6.1 CLOCK

两个时钟源: RC8M、RC32K, 系统时钟结构图如下所示:

图 6 时钟结构图

当 OPTION 选项中 BDGC\_ID=1 时,BANDGAP 修调无效; 当 OPTION 选项中 BDGC\_ID=0 时,BANDGAP 修调有效; 修调配置寄存器为:

#### • BANDGAP 调整寄存器(BDGC, 1098h):

| BIT     | Bit7 | Bit6      | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |  |

|---------|------|-----------|------|------|------|------|------|------|--|--|--|

| Name    |      | BDGC[7:0] |      |      |      |      |      |      |  |  |  |

| Access  |      |           |      | !    | R/W  |      |      |      |  |  |  |

| Default |      |           |      | (    | Dxxx |      |      |      |  |  |  |

Bit[7:0] BDGC: 内部 BANDGAP 调整寄存器(BANDGAP Calibration)

说明: BDGC 读的值是 OPT\_BG 的 8 位,不是 BDGC 寄存器的值

#### 6.2 工作模式

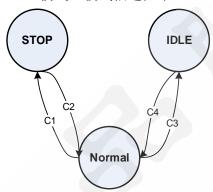

支持 Normal 模式、STOP 模式、IDLE 模式,模式描述如下:

C1:执行STOP指令 C2:从STOP模式唤醒 C3:执行IDLE指令 C4:从IDLE模式唤醒

图 7 工作模式转换图

- STOP 模式下, CPU 及外设都停止工作, PD 位清零, TO 位置 1, 看门狗清零同时保持运行状态, RC8M 停振, I/O 维持原状:

- ▶ 外部中断 0 低电平、外部中断 1 低电平可唤醒 STOP 模式。

- ▶ WDT 溢出可唤醒 STOP 模式。

- ▶ IO 口电平变化可唤醒 STOP 模式。

- IDLE 模式下,除 CPU 外,其它外设都可工作:

- ▶ 所有中断都可唤醒 IDLE 模式。

- ▶ WDT溢出可唤醒 IDLE模式。

- ▶ IO 口电平变化可唤醒 IDLE 模式。

#### **6.3 INT**

系统有6种中断源:

- 1) 定时器 T0 溢出中断

- 2) 定时器 T1 溢出中断

- 3) INTO 中断

- 4) INT1 中断

- 5) ADC 中断

- 6) 触摸中断

#### 6.3.1中断功能

- 1. IF0/1 为中断标志寄存器,决定该寄存器所发生的中断状态。IE0/IE1 为中断使能寄存器。IPEN 为中断优先级控制寄存器。

- 2. 中断允许总控位 GIE/GIEL 有两个功能: 当 IPEN 为低电平时,其为全局中断使能位;当 IPEN 为高电平时,其为低优先级中断全局使能位。

- 3. 中断允许总控位 GIEH: 当 IPEN 为高电平时,其为高优先级中断全局使能位。

- 4. 支持两种中断优先级(高和低),所有中断源都可单独配置为高优先级或低优先级。允许低优先级中断服务程序嵌套高优先级中断服务程序,不允许同优先级之间的中断嵌套。

- 5. 两个中断入口地址: 008h 和 018h。当 IPEN 为低电平时,入口地址为 008h; 当 IPEN 为高电平时,默认入口地址为 008h(所有中断源默认为低优先级),当某个中断源切换到高优先级时,中断入口地址切换到 018h。

- 6. 进入中断服务程序前,PC、ACC、STATUS及 DPAGE 会被压栈保护。

- 7. 当中断优先级 IPEN 为低电平时,所有中断源都为低优先级(软件错误地配置为高优先级时,硬件将强行将其变为低优先级)。

- 8. call 指令堆栈满后产生中断,中断不会立即响应,需要等到 call 指令出栈后再响应中断。

- 9. call 指令 7 级堆栈后,产生低优先级中断,在低优先级中断处理过程中高优先级中断无法响应。

#### 6.3.2中断寄存器

中断模块相关寄存器:

| 地址    | 符号    | Bit7     | Bit6 | Bit5 | Bit4   | Bit3   | Bit2  | Bit1  | Bit0  | 复位值       |

|-------|-------|----------|------|------|--------|--------|-------|-------|-------|-----------|

| 108Bh | IE0   | GIE/GIEL | GIEH | -    | INT1IE | INT0IE | -     | T1IE  | TOIE  | 00-0 0-00 |

| 108Ch | IF0   | -        | -    | -    | INT1IF | INT0IF | -     | T1IF  | T0IF  | 0 0-00    |

| 108Dh | IE1   | -        | -    | -    | -      | -      | -     | ADCIE | THIE  | 00        |

| 108Eh | IF1   | -        | -    | -    | -      | -      | -     | ADCIF | THIF  | 00        |

| 1091h | IP0   | IPEN     | -    | -    | INT1IP | INT0IP | -     | T1IP  | T0IP  | 00 0-00   |

| 1092h | IP1   | -        | -    | -    | -      | -      | -     | ADCIP | THIP  | 00        |

| 1094h | INTS  | -        | -    | -    | -      | INT1S  | [1:0] | INT0S | [1:0] | 0000      |

| 1095h | INTEN | -        | -    | -    | _      | -      | -     | EINT[ | [1:0] | 00        |

#### • 中断屏蔽寄存器 0(IE0, 108Bh):

| BIT     | Bit7     | Bit6 | Bit5 | Bit4   | Bit3   | Bit2 | Bit1 | Bit0 |

|---------|----------|------|------|--------|--------|------|------|------|

| Name    | GIE/GIEL | GIEH | 1    | INT1IE | INT0IE | 1    | T1IE | T0IE |

| Access  | R/W      | R/W  | -    | R/W    | R/W    | -    | R/W  | R/W  |

| Default | 0        | 0    | -    | 0      | 0      | -    | 0    | 0    |

Bit[7] GIE/GIEL: 中断允许控制位

当 IPEN 为低电平时:

1: 使能所有没有屏蔽的中断

0: 禁止所有中断

当 IPEN 为高电平时:

1: 使能所有低优先级中断

0: 禁止所有低优先级中断

Bit[6] GIEH: 高优先级中断允许控制位

1: 使能所有高优先级中断

0: 禁止所有高优先级中断

Bit[4] INT1IE: INT1 中断屏蔽位

1: 使能外部中断 1

0: 禁止外部中断 1

Bit[3] INTOIE: INTO中断屏蔽位

1: 使能外部中断 0

0: 禁止外部中断 0

Bit[1] T1IE: TIMER1 溢出中断屏蔽位

1: 使能 TIMER1 溢出中断

0: 禁止 TIMER1 溢出中断

Bit[0] **TOIE:** TIMERO 溢出中断屏蔽位

1: 使能 TIMERO 溢出中断

0: 禁止 TIMER0 溢出中断

#### • 中断屏蔽寄存器 1(IE1, 108Dh):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1  | Bit0 |

|---------|------|------|------|------|------|------|-------|------|

| Name    | -    | -    | _    | -    | -    | -    | ADCIE | THIE |

| Access  | -    | -    | -    | -    | -    | -    | R/W   | R/W  |

| Default | -    | -    | -    | -    | -    | -    | 0     | 0    |

Bit[1] ADCIE: ADC 中断屏蔽位

1: 使能 ADC 中断

0: 禁止 ADC 中断

Bit[0] THIE: 触摸中断屏蔽位

1: 使能触摸中断

0: 禁止触摸中断

#### • 中断标志寄存器 0(IF0, 108Ch):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4   | Bit3   | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|--------|--------|------|------|------|

| Name    | -    | -    | -    | INT1IF | INT0IF | ı    | T1IF | T0IF |

| Access  | -    | -    | -    | R/W    | R/W    | -    | R/W  | R/W  |

| Default | -    | -    | -    | 0      | 0      | -    | 0    | 0    |

Bit[4] **INT1IF:** 外部中断 1 标志,软件写 0 清,写 1 无效

Bit[3] **INTOIF**: 外部中断 0 标志, 软件写 0 清, 写 1 无效

Bit[1] **T1IF**: TIMER1 溢出中断标志,软件写 0 清,写 1 无效

Bit[0] **TOIF:** TIMERO 溢出中断标志,软件写 0 清,写 1 无效

#### 中断标志寄存器 1(IF1, 108Eh):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1  | Bit0 |

|---------|------|------|------|------|------|------|-------|------|

| Name    | -    | -    | 1    | -    | -    | -    | ADCIF | THIF |

| Access  | -    | -    | -    | -    | -    | -    | R/W   | R/W  |

| Default | -    | -    | -    | -    | -    | -    | 0     | 0    |

Bit[1] ADCIF: ADC 中断标志, 软件写 0 清, 写 1 无效

Bit[0] THIF: 触摸中断标志,软件写 0 清,写 1 无效

#### • 中断优先级控制寄存器 0(IP0, 1091h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4   | Bit3   | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|--------|--------|------|------|------|

| Name    | IPEN | _    | -    | INT1IP | INT0IP | -    | T1IP | T0IP |

| Access  | R/W  | -    | -    | R/W    | R/W    | -    | R/W  | R/W  |

| Default | 0    | -    | -    | 0      | 0      | -    | 0    | 0    |

Bit[7] IPEN: 中断优先级使能位

1: 使能中断优先级

0: 禁止中断优先级

Bit[4] INT1IP: INT1中断优先级选择位

1: INT1 中断为高优先级

0: INT1 中断为低优先级

Bit[3] INTOIP: INTO 中断优先级选择位

1: INTO 中断为高优先级

0: INT0 中断为低优先级

Bit[1] **T1IP:** T1 中断优先级选择位

1: T1 中断为高优先级

0: T1 中断为低优先级

Bit[0] TOIP: TO 中断优先级选择位

1: T0 中断为高优先级

0: T0 中断为低优先级

#### • 中断优先级控制寄存器 1(IP1, 1092h):

| BIT    | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1  | Bit0 |

|--------|------|------|------|------|------|------|-------|------|

| Name   | -    | 1    | -    | 1    | 1    | -    | ADCIP | THIP |

| Access | -    | 1    | -    | 1    | 1    | -    | R/W   | R/W  |

|         |   |   |   |   |   | 1 |   |   |

|---------|---|---|---|---|---|---|---|---|

| Default | - | - | - | - | - | - | 0 | 0 |

Bit[1] ADCIP: ADC 中断优先级选择位

1: ADC 中断为高优先级

0: ADC 中断为低优先级

Bit[0] THIP: 触控中断优先级选择位

1: 触控中断为高优先级

0: 触控中断为低优先级

#### • 外部中断触发方式选择寄存器(INTS, 1094h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4       | Bit3 | Bit2       | Bit1 | Bit0 |

|---------|------|------|------|------------|------|------------|------|------|

| Name    |      |      | -    | INT1S[1:0] |      | INT0S[1:0] |      |      |

| Access  | -    |      | -    |            | R/W  |            | R/   | W    |

| Default | -    | -    | -    |            | 00   |            | 0    | 0    |

Bit[3:2] INT1S: 外部中断 1 触发方式选择

00: 低电平触发

01: 下降沿触发

10: 上升沿触发

11: 下降沿或上升沿触发

Bit[1:0] INTOS: 外部中断 0 触发方式选择

00: 低电平触发

01: 下降沿触发

10: 上升沿触发

11: 下降沿或上升沿触发

#### • 外部中断触发方式选择寄存器(INTEN, 1095h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1      | Bit0 |

|---------|------|------|------|------|------|------|-----------|------|

| Name    | -    | -    | -    |      | -    |      | EINT[1:0] |      |

| Access  | -    |      | -    |      | -    |      | R/        | W    |

| Default | -    |      | -    |      | -    |      | 00        |      |

Bit[1:0] **EINT:** 外部中断使能选择

Bit[1]: 外部中断 1 使能,高有效 Bit[0]: 外部中断 0 使能,高有效

- 说明: 当系统从中断子程序返回时需要将对应的中断标志位清零,只能采用如下几种方式:

- 1. MOV 指令清相应的中断标志位。以清 TOIF 为例,清除方法如下所示:

MOV A, #0xFE

MOV IF0,A

- 2. BCLR 指令清相应的中断标志位。以清 T0IF 为例,清除方法如下所示: BCLR IF0.0

- 3. ANDR, XORR 指令清相应中断标志位。以清 TOIF, 且用 ANDR 指令为例, 清除方法如下所示: MOV A, #0xFE ANDR A, IF0

#### **6.4 GPIO**

共有两组 GPIO 口, 共 14 个 I/O 口, 其中 P0 口为 6 脚 I/O 口 (P05 只有输入功能), P1 口为 8 脚 I/O 口。

GPIO 模块相关寄存器:

| 地址    | 符号   | Bit7 | Bit6 | Bit5      | Bit4        | Bit3      | Bit2   | Bit1 | Bit0 | 复位值       |

|-------|------|------|------|-----------|-------------|-----------|--------|------|------|-----------|

| 1099h | P0   | İ    | ı    |           |             | P0[5:0]   |        |      |      | xx xxxx   |

| 109Ah | P0OD | -    | 1    | -         |             | P0OI      | D[4:0] |      |      | 0 0000    |

| 109Bh | P0PH | -    | -    |           |             | P0PH[5:0] |        |      |      | 11 1111   |

| 109Ch | P0PD | -    | -    |           |             | P0PD[5:0] | 7      |      |      | 00 0000   |

| 109Dh | P00E | -    | -    | -         | - P0OE[4:0] |           |        |      |      |           |

| 109Fh | P0WK | -    | -    |           |             | P0WK[5:0] |        |      |      | 00 0000   |

| 10A0h | P1   |      |      |           | P1[7:       | 0]        |        |      |      | xxxx xxxx |

| 10A1h | P10D |      |      |           | P10D[       | 7:0]      |        |      |      | 0000 0000 |

| 10A2h | P1PH |      |      |           | P1PH[       | 7:0]      |        |      |      | 1111 1111 |

| 10A3h | P1PD |      |      | P1PD[7:0] |             |           |        |      |      | 0000 0000 |

| 10A4h | P10E |      |      | P10E[7:0] |             |           |        |      |      | 1111 1111 |

| 10A6h | P1WK |      |      | P1WK[7:0] |             |           |        |      |      | 0000 0000 |

#### • P0 端口读写数据寄存器(P0, 1099h):

| BIT     | Bit7 | Bit6 | Bit5  | Bit4 | Bit3 | Bit2  | Bit1 | Bit0 |  |

|---------|------|------|-------|------|------|-------|------|------|--|

| Name    | -    | -    | P0[5] |      |      | P0[i] |      |      |  |

| Access  | -    | -    | R     | R/W  |      |       |      |      |  |

| Default | -    | -    | х     |      |      | xxxxx |      |      |  |

Bit[5:0] **P0[i]:** P0[i]端口读写数据

读该寄存器:如果是做输入时,读的数据是外部输入;如果是做输出时,读的数据是 P0 寄存器值写该端口,为输出模式时写数据从 PAD 输出

说明: P0[5]为只读,不可写。

#### • P1 端口读写数据寄存器(P1, 10A0h):

| BIT     | Bit7 | Bit6  | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|-------|------|------|------|------|------|------|--|--|

| Name    |      | P1[i] |      |      |      |      |      |      |  |  |

| Access  |      | R/W   |      |      |      |      |      |      |  |  |

| Default |      | 0xxx  |      |      |      |      |      |      |  |  |

Bit[7:0] **P1[i]:** P1[i]端口读写数据

读该寄存器:如果是做输入时,读的数据是外部输入;如果是做输出时,读的数据是 P1 寄存器值写该端口,为输出模式时写数据从 PAD 输出

#### • P0 开漏控制寄存器(P0OD, 109Ah):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4      | Bit3 | Bit2  | Bit1 | Bit0 |  |

|---------|------|------|------|-----------|------|-------|------|------|--|

| Name    |      | -    |      | P0OD[ i ] |      |       |      |      |  |

| Access  |      | -    |      | R/W       |      |       |      |      |  |

| Default |      | -    |      |           |      | 00000 |      |      |  |

Bit[4:0] **P0OD[i]:** P0[i]开漏使能

1: 使能

0: 禁止

# • P1 开漏控制寄存器(P1OD, 10A1h):

| BIT     | Bit7 | Bit6      | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|-----------|------|------|------|------|------|------|--|--|

| Name    |      | P10D[ i ] |      |      |      |      |      |      |  |  |

| Access  |      | R/W       |      |      |      |      |      |      |  |  |

| Default |      |           |      | 0x   | 00   |      |      |      |  |  |

Bit[7:0] **P1OD[i]:** P1[i]开漏使能

1: 使能

0: 禁止

# • P0 上拉电阻控制寄存器(P0PH, 109Bh):

| BIT     | Bit7 | Bit6 | Bit5   | Bit4 | Bit3      | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|------|--------|------|-----------|------|------|------|--|--|

| Name    | -    | -    |        |      | P0PH[ i ] |      |      |      |  |  |

| Access  | -    | -    |        |      | R/        | W    |      |      |  |  |

| Default | -    | -    | 111111 |      |           |      |      |      |  |  |

Bit[5:0] POPH[i]: PO[i]内部上拉使能

1: 禁止

0: 使能

### • P1 上拉电阻控制寄存器(P1PH, 10A2h):

| BIT     | Bit7 | Bit6      | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |

|---------|------|-----------|------|------|------|------|------|------|--|

| Name    |      | P1PH[ i ] |      |      |      |      |      |      |  |

| Access  |      | R/W       |      |      |      |      |      |      |  |

| Default |      | 0xFF      |      |      |      |      |      |      |  |

Bit[7:0] **P1PH[i]:** P1[i]内部上拉使能

1: 禁止

0: 使能

### • P0 下拉电阻使能寄存器(P0PD, 109Ch):

| BIT     | Bit7 | Bit6 | Bit5      | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |  |

|---------|------|------|-----------|------|------|------|------|------|--|--|--|

| Name    | -    | -    | P0PD[ i ] |      |      |      |      |      |  |  |  |

| Access  | -    | -    | R/W       |      |      |      |      |      |  |  |  |

| Default | -    | -    |           |      | 000  | 000  |      |      |  |  |  |

Bit[5:0] **P0PD[i]:** P0[i]的下拉电阻使能

1: 使能下拉电阻

0: 禁止下拉电阻

### • P1 下拉电阻使能寄存器(P1PD, 10A3h):

| BIT     | Bit7 | Bit6      | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|-----------|------|------|------|------|------|------|--|--|

| Name    |      | P1PD[ i ] |      |      |      |      |      |      |  |  |

| Access  |      |           |      | R/   | W    |      |      |      |  |  |

| Default |      |           |      | 0x   | 00   |      |      |      |  |  |

Bit[7:0] **P1PD[i]:** P1[i]的下拉电阻使能

1: 使能下拉电阻

0: 禁止下拉电阻

#### • P0 I/O 方向控制寄存器(P0OE, 109Dh):

POOE 设为"1"表示该脚为输入(高阻抗),设为"0"表示该脚为输出,POOE 寄存器可读写,系统复位以后设置为输入(高阻抗)。

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2      | Bit1 | Bit0 |

|---------|------|------|------|------|------|-----------|------|------|

| Name    | -    | -    | -    |      |      | P00E[4:0] |      |      |

| Access  | -    | -    | -    |      |      | R/W       |      |      |

| Default | -    | -    |      |      |      | 11111     |      |      |

#### • P1 I/O 方向控制寄存器(P1OE, 10A4h):

P1OE 设为"1"表示该脚为输入(高阻抗),设为"0"表示该脚为输出,P1OE 寄存器可读写,系统复位以后设置为输入(高阻抗)。

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3   | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|------|--------|------|------|------|

| Name    |      |      |      | P10  | E[ i ] |      |      |      |

| Access  |      |      |      | R    | W .    |      |      |      |

| Default |      |      |      | 0x   | FF     |      |      |      |

# • P0 唤醒模式使能(P0WK, 109Fh):

| BIT     | Bit7 | Bit6 | Bit5      | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |

|---------|------|------|-----------|------|------|------|------|------|--|

| Name    | -    | -    | P0WK[ i ] |      |      |      |      |      |  |

| Access  | -    | -    | R/W       |      |      |      |      |      |  |

| Default | -    | -    | 000000    |      |      |      |      |      |  |

Bit[5:0] POWK[i]: PO 电平变化唤醒使能,只有配置为通用 GPIO 功能输入时才有效

1: 使能唤醒

0: 禁止唤醒

### • P1 唤醒模式使能(P1WK, 10A6h):

| - 7th Dt. |      |      |      |      |         |      |      |      |

|-----------|------|------|------|------|---------|------|------|------|

| BIT       | Bit7 | Bit6 | Bit5 | Bit4 | Bit3    | Bit2 | Bit1 | Bit0 |

| Name      |      |      |      | P1W  | 'K[ i ] |      |      |      |

| Access    |      |      |      | R/   | W       |      |      |      |

| Default   |      |      |      | 0x   | 00      |      |      |      |

Bit[7:0] P1WK[i]: P1 电平变化唤醒使能,只有配置为通用 GPIO 功能输入时才有效

- 1: 使能唤醒

- 0: 禁止唤醒

#### 说明:

- 1) P0/P1 有相应的上拉/下控制位(P0PH/P0PD/P1PH/P1PD 寄存器)来设置使能内部上拉。如果设置为输出模式,内部上拉/下拉功能会自动关闭。

- 2) P0/P1 有相应的开漏控制位(P0OD/P1OD 寄存器)来设置使能开漏输出。当开漏配置有效且数据寄存器值为 1 时,即使配置为输出模式,上拉功能也可以开启。

#### 6.5 TIMER

#### 6.5.1TIMER0

定时器 0 为 8 位向上定时器, 其从 TOOVR 开始计数, 当其计数值达到 0xFF 后, 产生 T0 溢出信号。 其特性如下:

- 1. 支持时钟预分频功能;

- 2. 定时功能;

#### TIMER0 模块相关寄存器:

| 地址    | 符号     | Bit7 | Bit6       | Bit5 | Bit4 | Bit3 | Bit2   | Bit1 | Bit0      | 复位值       |

|-------|--------|------|------------|------|------|------|--------|------|-----------|-----------|

| 10B6h | T0CON0 | -    | -          | -    | 1    | Т    | 0FS[2: | 0]   | T0EN      | 0000      |

| 10B9h | T0C    |      | T0C[7:0]   |      |      |      |        |      |           | 0000 0000 |

| 10BAh | T00VR  |      | T0OVR[7:0] |      |      |      |        |      | XXXX XXXX |           |

### • TIMER0 控制寄存器(T0CON0, 10B6h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|------|------|------|------|------|

| Name    | -    | -    | -    | -    |      | T0EN |      |      |

| Access  | -    | -    | -    | -    |      |      | R/W  |      |

| Default | -    | -    | -    | -    | 0.0  | 000  |      | 0    |

Bit[3:1] TOFS: TIMERO 工作于定时模式时时钟分频选择

000: 不分频

001: 2分频

010: 4分频

011: 8分频

100: 16 分频

101: 32 分频

110: 64 分频

111: 128 分频

Bit[0] TOEN: TIMERO 使能位

1: 使能 TIMER0

0: 禁止 TIMER0

# • 定时器计数值(T0C, 10B9h):

| BIT     | Bit7 | Bit6     | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|----------|------|------|------|------|------|------|--|--|

| Name    |      | T0C[7:0] |      |      |      |      |      |      |  |  |

| Access  |      |          |      | F    | ₹    |      |      |      |  |  |

| Default |      |          |      | 0x   | 00   |      |      |      |  |  |

Bit[7:0] **T0C[7:0]:** TIMER0 计数值

# • 定时器计数周期值(T0OVR, 10BAh):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3   | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|------|--------|------|------|------|

| Name    |      |      |      | T00V | R[7:0] |      |      |      |

| Access  |      |      |      | R/   | W      |      |      |      |

| Default |      |      |      | 0x   | XX     |      |      |      |

Bit[7:0] **T0OVR[7:0]:** 预设置的定时周期寄存器,实际定时周期为: **0xFF-T0OVR+1**(不能设置为 **0xFF)**

#### 1. 定时模式

TIMER0 能被配置为普通的定时模式,当 TIMER0 被启动后,定时周期寄存器 TOOVR 的值将会被 装载到定时器中,当定时器的计数器计满后将产生 TIMER0 溢出信号,同时 TOOVR 将会由硬件重新自动装载到计数器中。

#### TIMER0 工作于定时模式时的配置流程如下:

- 1. 配置时钟源选择 TOCKS

- 2. 配置 TOOVR;

- 3. 使能 TIMERO;

- 4. 计满溢出后,产生溢出信号。

#### 6.5.2TIMER1

TIMER1 为 10 位向上定时器, 其从 T1OVR 开始计数, 当其计数值达到 0x3FF 后, 产生 T1 溢出信号。其特性如下:

- 1. 支持时钟预分频功能;

- 2. 定时功能;

- 3. 5 路独立的 PWM 输出。

#### TIMER1 相关 SFR 描述如下:

|        | ,,,,   |      | (加及州) |      |        |            |           |        |         |           |  |

|--------|--------|------|-------|------|--------|------------|-----------|--------|---------|-----------|--|

| 地址     | 符号     | Bit7 | Bit6  | Bit5 | Bit4   | Bit3       | Bit2      | Bit1   | Bit0    | 复位值       |  |

| 10BDh  | T1CON0 | 1    | - /   | -    | -      |            | T1FS[2:0] |        | T1EN    | 0000      |  |

| 10BEh  | T1CON1 | 1    | -     | -    | PWM4EN | PWM3EN     | PWM2EN    | PWM1EN | PWM0EN  | 0 0000    |  |

| 10BFh  | T1CON2 | - (  | -     | -    | PWM4S  | PWM3S      | PWM2S     | PWM1S  | PWM0S   | 0 0000    |  |

| 10C0h  | T10VRL |      |       |      | Т      | 10VRL[7:0  | 0]        |        |         | xxxx xxxx |  |

| 10C1h  | T10VRH | -    | -     | -    | -      | -          | -         | T10VF  | RH[1:0] | XX        |  |

| 10C2h  | T1CL   |      |       |      |        | T101 [7:0] |           |        |         | 0000      |  |

| 100211 | TICL   |      |       |      |        | T1CL[7:0]  |           |        |         | 0000      |  |

| 10C3h  | T1CH   | 1    | 1     | -    | -      | -          | -         | T1Cl   | H[1:0]  | 00        |  |

| 10C4h  | T1D0L  |      |       |      |        | T1D0L[7:0] |           |        |         | XXXX XXXX |  |

| 10C5h  | T1D0H  | -    | -     | -    | -      | -          | -         | T1D0   | H[1:0]  | XX        |  |

| 10C6h  | T1D1L  |      |       |      |        | T1D1L[7:0] |           |        |         | xxxx xxxx |  |

| 10C7h  | T1D1H  | -    | -     | -    | -      | -          | -         | T1D1   | H[1:0]  | XX        |  |

| 10C8h  | T1D2L  |      |       |      |        | T1D2L[7:0] |           |        |         | xxxx xxxx |  |

| 10C9h  | T1D2H  | -    | -     | -    | -      | -          | -         | T1D2   | H[1:0]  | XX        |  |

| 10CAh  | T1D3L  |      |       |      |        | T1D3L[7:0] |           |        |         | xxxx xxxx |  |

| 10CBh  | T1D3H  | -    | -     | -    | -      | -          | -         | T1D3   | H[1:0]  | xx        |  |

| 10CCh  | T1D4L  |      |       |      |        | T1D4L[7:0] |           |        |         | xxxx xxxx |  |

| 10CDh  | T1D4H  | -    | -     | -    | -      | -          | -         | T1D4   | H[1:0]  | XX        |  |

# • TIMER1 控制寄存器 0(T1CON0, 10BDh):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|------|------|------|------|------|

| Name    | -    | -    | -    | -    |      | T1EN |      |      |

| Access  | -    | -    | -    | -    | R/W  |      |      | R/W  |

| Default | -    | -    | -    | -    | 000  |      |      | 0    |

Bit[3:1] **T1FS:** 定时器 1 时钟分频选择

000: 不分频

001: 2分频

010: 4分频

011: 8 分频

100: 16 分频

101: 32 分频

110:64 分频

111: 128 分频

Bit[0] T1EN: TIMER1 使能位

1: 使能 TIMER1

0: 禁止 TIMER1

#### • TIMER1 控制寄存器 1(T1CON1, 10BEh):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|---------|------|------|------|--------|--------|--------|--------|--------|

| Name    | -    | 1    | -    | PWM4EN | PWM3EN | PWM2EN | PWM1EN | PWM0EN |

| Access  | -    | -    | -    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Default | -    | -    | -    | 0      | 0      | 0      | 0      | 0      |

#### Bit[4] PWM4EN: Timer1 PWM4 使能位

1: 使能 Timer1 PWM4 输出

0: 关闭 Timer1 PWM4 输出

#### Bit[3] PWM3EN: Timer1 PWM3 使能位

1: 使能 Timer1 PWM3 输出

0: 关闭 Timer1 PWM3 输出

#### Bit[2] PWM2EN: Timer1 PWM2 使能位

1: 使能 Timer1 PWM2 输出

0: 关闭 Timer1 PWM2 输出

#### Bit[1] PWM1EN: Timer1 PWM1 使能位

1: 使能 Timer1 PWM1 输出

0: 关闭 Timer1 PWM1 输出

#### Bit[0] PWM0EN: Timer1 PWM0 使能位

1: 使能 Timer1 PWM0 输出

0: 关闭 Timer1 PWM0 输出

#### • TIMER1 控制寄存器 2(T1CON2, 10BFh):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

|---------|------|------|------|-------|-------|-------|-------|-------|

| Name    | _    | _    | -    | PWM4S | PWM3S | PWM2S | PWM1S | PWM0S |

| Access  | -    | -    | -    | R/W   | R/W   | R/W   | R/W   | R/W   |

| Default | -    | -    | -    | 0     | 0     | 0     | 0     | 0     |

#### Bit[4] PWM4S: Timer1 PWM4 输出有效电平选择位

1: 先输出低电平, 占空比为低电平宽度

0: 先输出高电平, 占空比为高电平宽度

#### Bit[3] PWM3S: Timer1 PWM3 输出有效电平选择位

1: 先输出低电平, 占空比为低电平宽度

0: 先输出高电平, 占空比为高电平宽度

#### Bit[2] PWM2S: Timer1 PWM2 输出有效电平选择位

1: 先输出低电平, 占空比为低电平宽度

0: 先输出高电平, 占空比为高电平宽度

#### Bit[1] PWM1S: Timer1 PWM1 输出有效电平选择位

1: 先输出低电平, 占空比为低电平宽度

0: 先输出高电平,占空比为高电平宽度

#### Bit[0] PWM0S: Timer1 PWM0 输出有效电平选择位

1: 先输出低电平,占空比为低电平宽度

0: 先输出高电平, 占空比为高电平宽度

#### TIMER1 预设置的周期寄存器(T10VRL, 10C0h):

| BIT     | Bit7 | Bit6        | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |

|---------|------|-------------|------|------|------|------|------|------|--|

| Name    |      | T10VRL[7:0] |      |      |      |      |      |      |  |

| Access  |      | R/W         |      |      |      |      |      |      |  |

| Default |      |             |      | 0x   | xx   |      |      |      |  |

Bit[7:0] **T1OVRL[7:0]:** TIMER1 预设置的周期寄存器低 8 位

#### • TIMER1 预设置的周期寄存器(T1OVRH, 10C1h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2    | Bit1  | Bit0    |

|---------|------|------|------|------|------|---------|-------|---------|

| Name    | -    | -    | -    | -    | -    | //-     | T10VF | RH[1:0] |

| Access  | -    | -    | -    | -    | -    | -       | R/    | W       |

| Default | -    | -    | -    | -    |      | <u></u> | x     | X       |

Bit[1:0] **T1OVRH[1:0]:** TIMER1 预设置的周期寄存器高 2 位

实际周期为: 0x3FF -{T10VRH, T10VRL}+1

#### • TIMER1 计数寄存器(T1CL, 10C2h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3   | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|------|--------|------|------|------|

| Name    |      |      |      | T1CI | _[7:0] |      |      |      |

| Access  |      |      |      | I    | ٦      |      |      |      |

| Default |      |      |      | 0×   | 00     |      |      |      |

Bit[7:0] **T1CL[7:0]:** TIMER1 计数值低 8 位

#### • TIMER1 计数寄存器(T1CH, 10C3h):

| ВІТ     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0   |

|---------|------|------|------|------|------|------|------|--------|

| Name    | -    | -    | -    | -    | -    | -    | T1CH | H[1:0] |

| Access  | -    | -    | -    | -    | -    | -    | R    |        |

| Default | -    | -    | -    | -    | -    | -    | 00   |        |

Bit[1:0] **T1CH[1:0]:** TIMER1 计数值高 2 位

实际计数值为: {T1CH,T1CL}

#### • TIMER1 PWM0 占空比设置寄存器(T1D0L, 10C4h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3   | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|------|--------|------|------|------|

| Name    |      |      |      | T1D0 | L[7:0] |      |      |      |

| Access  |      |      |      | R/   | W      |      |      |      |

| Default | 0xxx |      |      |      |        |      |      |      |

Bit[7:0] **T1D0L[7:0]:** PWM0 占空比低 8 位, TIMER1 PWM 模式时, PWM0 实际占空比为: ({T1D0H,T1D0L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

#### • TIMER1 PWM0 占空比设置寄存器(T1D0H, 10C5h):

|         |      |      | •    |      |      |      |      |        |

|---------|------|------|------|------|------|------|------|--------|

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0   |

| Name    | -    | -    | -    | -    | -    | -    | T1D0 | H[1:0] |

| Access  | -    | -    | -    | -    | -    | -    | R/   | W      |

| Default | -    | -    | -    | -    | -    | -    | х    | X      |

Bit[1:0] T1D0H[1:0]: PWM0 占空比高 2 位, TIMER1 PWM 模式时, PWM0 实际占空比为:

({T1D0H,T1D0L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

#### • TIMER1 PWM1 占空比设置寄存器(T1D1L, 10C6h):

| BIT     | Bit7 | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------|------------|------|------|------|------|------|------|

| Name    |      | T1D1L[7:0] |      |      |      |      |      |      |

| Access  |      | R/W        |      |      |      |      |      |      |

| Default |      |            |      | 0x   | XX   |      |      |      |

Bit[7:0] **T1D1L[7:0]:** PWM1 占空比低 8 位, TIMER1 PWM 模式时, PWM1 实际占空比为: ({T1D1H,T1D1L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

#### • TIMER1 PWM1 占空比设置寄存器(T1D1H, 10C7h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0   |

|---------|------|------|------|------|------|------|------|--------|

| Name    | -    | -    | -    | _    | -    | -    | T1D1 | H[1:0] |

| Access  | -    | -    | -    | -    | J    | -    | R/W  |        |

| Default | -    | -    | -    | _    | -    | -    | х    | Х      |

Bit[1:0] **T1D1H[1:0]:** PWM1 占空比高 2 位, TIMER1 PWM 模式时, PWM1 实际占空比为: ({T1D1H,T1D1L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

#### • TIMER1 PWM2 占空比设置寄存器(T1D2L, 10C8h):

| BIT     | Bit7 | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------|------------|------|------|------|------|------|------|

| Name    |      | T1D2L[7:0] |      |      |      |      |      |      |

| Access  |      | R/W        |      |      |      |      |      |      |

| Default |      |            |      | 0x   | XX   |      |      |      |

Bit[7:0] **T1D2L[7:0]:** PWM2 占空比低 8 位, TIMER1 PWM 模式时, PWM2 实际占空比为: ({T1D2H,T1D2L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

#### • TIMER1 PWM2 占空比设置寄存器(T1D2H, 10C9h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0   |

|---------|------|------|------|------|------|------|------|--------|

| Name    | -    | -    | -    | -    | -    | -    | T1D2 | H[1:0] |

| Access  | -    | -    | _    | -    | -    | -    | R/W  |        |

| Default | -    | -    | -    | -    | -    | -    | xx   |        |

Bit[1:0] **T1D2H[1:0]:** PWM2 占空比高 2 位, TIMER1 PWM 模式时, PWM2 实际占空比为: ({T1D2H,T1D2L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

#### • TIMER1 PWM3 占空比设置寄存器(T1D3L, 10CAh):

| BIT     | Bit7       | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------------|------|------|------|------|------|------|------|

| Name    | T1D3L[7:0] |      |      |      |      |      |      |      |

| Access  | R/W        |      |      |      |      |      |      |      |

| Default | 0xxx       |      |      |      |      |      |      |      |

Bit[7:0] T1D3L[7:0]: PWM3 占空比低 8 位, TIMER1 PWM 模式时, PWM3 实际占空比为:

www.pintengtech.com 版本号 V1.4 36 / 53

({T1D3H,T1D3L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

#### • TIMER1 PWM3 占空比设置寄存器(T1D3H, 10CBh):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0   |

|---------|------|------|------|------|------|------|------|--------|

| Name    | -    | -    | -    | -    | -    | -    | T1D3 | H[1:0] |

| Access  | -    | -    | -    | -    | -    | -    | R/W  |        |

| Default | -    | -    | -    | -    | -    | -    | х    | X      |

Bit[1:0] **T1D3H[1:0]:** PWM3 占空比高 2 位, TIMER1 PWM 模式时, PWM3 实际占空比为: ({T1D3H,T1D3L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

# • TIMER1 PWM4 占空比设置寄存器(T1D4L, 10CCh):

| BIT     | Bit7 | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |  |

|---------|------|------------|------|------|------|------|------|------|--|--|--|

| Name    |      | T1D4L[7:0] |      |      |      |      |      |      |  |  |  |

| Access  |      | R/W        |      |      |      |      |      |      |  |  |  |

| Default |      |            |      | 0x   | xx   |      |      |      |  |  |  |

Bit[7:0] **T1D4L[7:0]:** PWM4 占空比低 8 位, TIMER1 PWM 模式时, PWM4 实际占空比为: ({T1D4H,T1D4L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

#### TIMER1 PWM4 占空比设置寄存器(T1D4H, 10CDh):

| BIT     | Bit7 | Bit6     | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0   |

|---------|------|----------|------|------|------|------|------|--------|

| Name    | -    | -        | -    | -    | -    | -    | T1D4 | H[1:0] |

| Access  | -    | <u>-</u> | -    | -    | -    | -    | R/W  |        |

| Default | -    | -        | -    | -    | -    | -    | Х    | X      |

Bit[1:0] **T1D4H[1:0]:** PWM4 占空比高 2 位, TIMER1 PWM 模式时, PWM4 实际占空比为: ({T1D4H,T1D4L}-{T1OVRH,T1OVRL}+1) / (0x3FF -{T1OVRH,T1OVRL} +1)

#### 1. 定时模式

定时器 TIMER1 能被配置为普通的定时模式,当 TIMER1 被启动后,定时周期寄存器的值将会被装载到定时器中,当定时器的计数器计满后将产生 TIMER1 溢出信号,同时周期寄存器将会由硬件重新自动装载到计数器中,然后启动向上计数。

#### TIMER1 工作于定时模式时的配置流程如下:

- 1. 配置时钟源选择 T1CKS

- 2. 配置 T1OVR;

- 3. 使能 TIMER1;

- 4. 计满溢出后,硬件产生 T1 溢出信号。

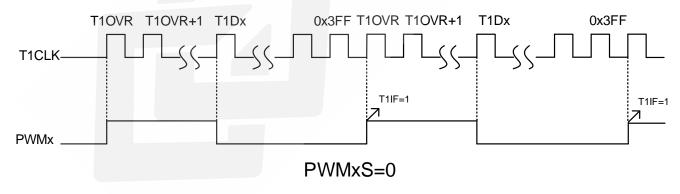

# 2. PWM 模式

定时器 TIMER1 能被配置为 PWM 模式,用于 5 路独立的 PWM 输出。其有自动装载功能,即当 TIMER1 被启动后,PWM 载波周期寄存器的值及 5 路 PWM 占空比的值将会被装载到定时器 TIMER1 中,当定时器计满后,PWM 载波周期寄存器及 5 路 PWM 占空比的值将会由硬件重新自动装载到计数器中,然后启动向上计数。

## TIMER1 工作于 PWM 模式时的配置流程如下:

- 1. 配置时钟源选择 T1CKS

- 2. 配置 T1OVR ,T1Dx;

- 3. 配置 PWMxS:

- 4. 使能 PWMxEN;

- 5. 使能 TIMER1;

周期为(0xFF-T1OVR+1), PWMx 高电平脉宽为 T1Dx。PWMx 波形输出如下:

图 8 PWM 输出时序图

# 6.6 LVD

提供 4 档电压检测(LVD)功能,当 LVD 检测有效,LVDCON.LVDOUT 标识将会自动置位为 1。

# • LVD 控制寄存器(LVDCON, 10F5h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3   | Bit2  | Bit1        | Bit0 |

|---------|------|------|------|------|--------|-------|-------------|------|

| Name    |      |      | -    |      | LVDOUT | LVDEN | LVDSEL[1:0] |      |

| Access  |      |      | -    |      | R      | R/W   | R           | /W   |

| Default | -    |      |      |      | 0      | 0     | (           | 00   |

Bit[3] LVDOUT: 低压检测标志位

1: 低压检测有效

0: 低压检测无效

Bit[2] LVDEN: 低电压检测使能位

1: 使能 LVD

0: 关闭 LVD

Bit[1:0] LVDSEL: 低电压检测点选择

00: 2.3V

01: 2.5V

10: 2.9V

11: 4.3V

# **6.7 TOUCH**

触摸模块(TOUCH)采用电容数字转换器(Cap Digtal Convertor, CDC)结构,把触摸通道的电容值转换为计数值,程序读取其数值后进行算法处理,实现稳定可靠的触摸按键检测,最多支持 12 个通道。

#### 6.8 ADC

集成了一个 12 位 SAR ADC, 相关 SFR 描述如下:

ADC 模块相关寄存器:

|       |        | 1          |      |                              |           |         |             |        |      |           |

|-------|--------|------------|------|------------------------------|-----------|---------|-------------|--------|------|-----------|

| 地址    | 符号     | Bit7       | Bit6 | Bit5                         | Bit4      | Bit3    | Bit2        | Bit1   | Bit0 | 复位值       |

| 10DBh | ADCON0 | ADCCK[2:0] |      |                              | ADCE      | А       | ADCSPT[3:0] |        |      | 0000 0000 |

| 10DCh | ADCON1 | ADCVO      | -    | -                            | ADCS      | ADCEN   | ADC         | VREF[2 | 2:0] | 00 0000   |

| 10DDh | ADCON2 | -          | -    | - ADCCUR ADCCALD ADCCAL[3:0] |           | 00 0000 |             |        |      |           |

| 10DEh | ADCON3 | -          | -    | -                            | -         | -       | ADC         | ADDR[  | 2:0] | 000       |

| 10DFh | ADCCH0 | -          | -    | -                            | -         | Α       | DCCH        | 0[3:0] |      | 0000      |

| 10E3h | ADCOL  |            |      |                              | ADCOL[7:0 | )]      | 4           |        |      | 0000 0000 |

| 10E4h | ADCOH  | -          | -    | -                            | -         | А       | DCOF        | H[3:0] |      | 0000      |

### ADC 控制寄存器 0(ADCON0, 10DBh):

| BIT     | Bit7 | Bit6       | Bit5 | Bit4 | Bit3        | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|------------|------|------|-------------|------|------|------|--|--|

| Name    | ,    | ADCCK[2:0] |      | ADCE | ADCSPT[3:0] |      |      |      |  |  |

| Access  | R/W  |            |      | R/W  | R/W         |      |      |      |  |  |

| Default |      | 000        |      | 0    | 0000        |      |      |      |  |  |

# Bit[7:5] ADCCK: ADC 时钟选择(ADC Clock)

000: f<sub>ADC</sub>=f<sub>RC8M</sub>

001: f<sub>ADC</sub>=f<sub>RC8M</sub> /2

010: fadc=frc8m /4

011: f<sub>ADC</sub>=f<sub>RC8M</sub> /8

100: fadc=frc8M /16

101: f<sub>ADC</sub>=f<sub>RC8M</sub> /32

110: fadc=frc8M /64

111: fadc=frc8m /128

### Bit[4] ADCE: ADC 转换完成标志位(ADC End)

1: ADC 转换完成,由软件清 0;每次重新启动 ADCS 时硬件会清 ADCE

0: ADC 转换未完成

#### Bit[3:0] ADCSPT: ADC 采样时间周期选择(ADC Sample Period)

采样时间=(ADCSPT[3:0]+1)\*T, T 为 ADC 时钟, 软件需配置此选项, 例如: ADCSPT[3:0]=8 ADC 转换完成时间=采样时间+比较时间(14 个 ADC 周期)=(ADCSPT[3:0]+1+14)\*T

#### • ADC 控制寄存器 1(ADCON1, 10DCh):

| BIT     | Bit7  | Bit6 | Bit5 | Bit4 | Bit3  | Bit2         | Bit1 | Bit0 |

|---------|-------|------|------|------|-------|--------------|------|------|

| Name    | ADCVO | -    | -    | ADCS | ADCEN | ADCVREF[2:0] |      |      |

| Access  | R/W   | -    | -    | R/W  | R/W   | R/W          |      |      |

| Default | 0     | -    | -    | 0    | 0     | 000          |      |      |

#### Bit[7] ADCVO: ADC 参考电压端口输入输出选择位(ADC Vref Output)

0: VREF 端口不输出参考电压

1: VREF 端口输出参考电压

(配置 VREF 端口输出参考电压前需要将 VREF 端口先配置成 ADC 通道)

### Bit[4] ADCS: ADC 转换启动位(ADC Start)

0: 未启动转换

1: 启动转换(硬件不会清0此位,由软件清0终止转换)

#### Bit[3] ADCEN: ADC 使能位(ADC Enable)

1: 使能 ADC

0: 禁止 ADC

# Bit[2:0] ADCVREF: ADC 参考电压选择位(ADC Vref Select)

000: 选择 VDD 做为参考电压

001: 选择外部参考电压 Vref

011: 选择内部基准电压 2.048V 做为参考电压

Others: 无参考电压

# • ADC 控制寄存器 2(ADCON2, 10DDh):

| BIT     | Bit7 | Bit6 | Bit5   | Bit4        | Bit3        | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|------|--------|-------------|-------------|------|------|------|--|--|

| Name    | -    | -    | ADCCUR | ADCCAL<br>D | ADCCAL[3:0] |      |      |      |  |  |

| Access  | -    | 1    | R/W    | R/W         | R/W         |      |      |      |  |  |

| Default | -    | -    | 0      | 0           | 00000       |      |      |      |  |  |

#### Bit[5] ADCCUR: ADC 电流选择位(ADC Current Select)

1: ADC 模块电流 0.5mA

0: ADC 模块电流 1mA

### Bit[4] ADCCALD: ADC 失调校准的校准方向(ADC Offset Calibration Direction)

1: 负向校准

0: 正向校准

#### Bit[3:0] ADCCAL: ADC 失调校准的校准值(ADC Offset Calibration)

失调电压值调整,绝对值越大,失调电压调整越大

#### ADC 控制寄存器 3(ADCON3, 10DEh):

| BIT     | Bit7 | Bit6 | Bit5     | Bit4         | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------|------|----------|--------------|------|------|------|------|

| Name    |      |      | -        | ADCADDR[2:0] |      |      |      |      |

| Access  |      |      | <u>-</u> | R/W          |      |      |      |      |

| Default |      |      | -        |              | 000  |      |      |      |

000: 选择外部输入通道 0 (ADC0)

001: 选择外部输入通道 1 (ADC1)

010: 选择外部输入通道 2 (ADC2)

011: 选择外部输入通道 3 (ADC3)

101: 选择内部特殊通道(内部 VDD/4)

110: 选择内部特殊通道(GND)

others: No define

www.pintengtech.com 版本号 V1.4 42 / 53

# ADC 通道配置寄存器 0(ADCCH0, 10DFh):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3        | Bit2 | Bit1 | Bit0 |  |

|---------|------|------|------|------|-------------|------|------|------|--|

| Name    | -    | -    | -    | -    | ADCCH0[3:0] |      |      |      |  |

| Access  | -    | -    | -    | -    | R/W         |      |      |      |  |

| Default | -    | -    | -    | -    | 0000        |      |      |      |  |

Bit[3] ADCCH0[3]: AD3 对应的 IO 口做为 ADC 功能,高电平有效 Bit[2] ADCCH0[2]: AD2 对应的 IO 口做为 ADC 功能,高电平有效 Bit[1] ADCCH0[1]: AD1 对应的 IO 口做为 ADC 功能,高电平有效 Bit[0] ADCCH0[0]: AD0 对应的 IO 口做为 ADC 功能,高电平有效

# • ADC 转换结果低 8 位寄存器(ADCOL, 10E3h):

| BIT     | Bit7 | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|------------|------|------|------|------|------|------|--|--|

| Name    |      | ADCOL[7:0] |      |      |      |      |      |      |  |  |

| Access  |      | R          |      |      |      |      |      |      |  |  |

| Default |      |            |      | 0x   | 00   |      |      |      |  |  |

Bit[7:0] ADCOL: ADC 转换结果低 8 位

# • ADC 转换结果高 4 位寄存器(ADCOH, 10E4h):

| BIT     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3       | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|------|------|------|------------|------|------|------|--|--|

| Name    | -    | -    | _    | -    | ADCOH[3:0] |      |      |      |  |  |

| Access  | -    | _    | -    | -    | R          |      |      |      |  |  |

| Default | -    | -    | -    |      | 0000       |      |      |      |  |  |

Bit[3:0] **ADCOH:** ADC 转换结果高 4 位

其与 ADCOL 组成 12 位转换结果值:{ADCOH[3:0], ADCOL[7:0]}

#### ADC 配置流程:

- 1. ADC 失调校准:上电时进行校准,只需校准一次。

- 1) 配置 ADC 时钟(ADCCK)和采样时间周期(ADCSPT)。

- 2) 配置 ADC 参考电压 ADCVREF 为内部基准。

- 3) 使能 ADC (ADCEN=1),设置输入通道为内部 GND。

- 4) 软件等待 100us 左右, 即等待 AD 初始化稳定。

- 5) 启动 ADC 连续转换。

- 6) 失调校准:

- a) 初始化校准量为正向校准最大值: ADCCON2[4:0]=0FH;

- b) 逐位从正向最大校准量调整到负向最大校准量,即 ADCCON2[4:0]校准顺序为 0FH→00H→10H→1FH,找到第一个 ADC 转换结果为 1 对应的校准量即为目标值,如果未找 到 1 值,则找 2 值。若两者均未找到则校准量 00H 为目标值

### 2. ADC 单次转换应用时的配置流程如下:

- 1) 配置 ADC 时钟(ADCCK)和采样时间周期(ADCSPT)。

- 2) 配置 ADC 通道 ADCCHx 和 ADCADDR。

- 3) 配置 ADC 参考电压 ADCVREF。

- 4) 使能 ADC (ADCEN=1), 如需中断则 ADCIE =1。

- 5) 软件等待 100us 左右, 即等待 AD 初始化稳定。

- 6) 配置 ADCON1 的 ADCS=1, 启动 ADC 转换, 直到软件清 0 才停止 ADC 转换。 不开 ADC 中断时: 判断 ADCE 是否置 1, 置 1 则可以读取 ADC 转换数据。 开 ADC 中断时: 直接进中断读取 ADC 转换数据。

- 7) 软件清 ADCE 及 ADCS, 完成一次 ADC 序列转换。

#### 3. ADC 连续转换应用时的配置流程如下:

- 1) 配置 ADC 时钟(ADCCK)和采样时间周期(ADCSPT)。

- 2) 配置 ADC 通道 ADCCHx 和 ADCADDR。

- 3) 配置 ADC 参考电压 ADCVREF。

- 4) 使能 ADC (ADCEN=1), 同时 ADC 中断也要打开 (ADCIE=1)。

- 5) 软件等待 100us, 即等待 AD 初始化稳定。

- 6) 配置 ADCON1 的 ADCS=1,启动 ADC 转换(连续转换时 ADCS 只需启动一次,以后一直保持为 1,软件清 0 才停止 ADC 转换),中断发生后进中断程序读取 ADC 转换数据。

#### **6.9 WDT**

看门狗定时器(WDT)无需任何外部电路即可工作,睡眠模式同样工作,启用看门狗使超时发生后 MCU 重启复位。

在一般操作或睡眠模式情况下,看门狗定时器溢出会导致 MCU 复位同时 TO 位被清零。

看门狗溢出时间可以通过配置选项 0 的 SUT[1:0]设置为 18ms、9ms、288ms、144ms,溢出周期变长可以通过设置 WDTCON .PS[2:0]使看门狗定时器分频最大达到 1:128,溢出周期最大为 36.8 秒。STOP 下的 WDT 溢出复位会导致芯片复位,在进睡眠之前还没完成的操作不会再继续。

CLRWDT 指令能使 WDT 和预置器清零。

STOP 指令能使 WDT 和预置器清零。

# WDT 相关寄存器:

### • WDT 控制寄存器(WDTCON, 1096h):

| BIT     | Bit7  | Bit6   | Bit5  | Bit4 | Bit3 | Bit2 | Bit1    | Bit0 |

|---------|-------|--------|-------|------|------|------|---------|------|

| Name    | LRCEN | WDTSEL | WDTEN | TO   | PD   |      | PS[2:0] |      |

| Access  | R/W   | R/W    | R/W   | R    | R    | R/W  |         |      |

| Default | 1     | 0      | 1     | 1    | 1    | 111  |         |      |

Bit[7] LRCEN: 内部 RC32K 时钟使能位

1: 使能 RC32K 时钟

0: 禁止 RC32K 时钟

Bit[6] WDTSEL: WDT 功能选择位

1: WDT 溢出唤醒,可以唤醒 IDLE 或 STOP 模式

0: WDT 溢出复位

Bit[5] WDTEN: WDT 使能位

1: 使能 WDT

0: 禁止 WDT

Bit[4] **TO:** 时间溢出标志

1: 当系统上电时或执行 "CLRWDT"或 "STOP"指令后

0: 看门狗定时器溢出

Bit[3] **PD:** Powerdown flag bit

1: 当系统上电时或执行"CLRWDT"指令后

0: 当执行"STOP"指令后

Bit[2:0] **PS[2:0]:** WDT 时钟分频选择控制位

000: WDT Rate=1:1

001: WDT Rate=1:2

010: WDT Rate=1:4

011: WDT Rate=1:8

100: WDT Rate=1:16

101: WDT Rate=1:32

110: WDT Rate=1:64

111: WDT Rate=1:128

# 6.10 复位方式

有 3 种复位方式:

- 1. 上电复位(POR): 上电过程中电压低于某一电压值使芯片保持复位,直到高于 POR 门限。

- 2. 低压复位(LVR): 当检测到电压低于某一电压值时会对芯片复位,保证芯片只在正常电压范围内工作

- 3. 看门狗 WDT 溢出复位:看门狗超时后 MCU 重启复位

根据不同的复位方式硬件对 TO 和 PD 位置 1 或清零。

### TO、PD 状态位影响事件

| No. | 事件                 | то | PD |

|-----|--------------------|----|----|

| 1   | Power-on           | 1  | 1  |

| 2   | WDT Time-Out       | 0  | u  |

| 3   | STOP instruction   | 1  | 0  |

| 4   | CLRWDT instruction | 1  | 1  |

#### 复位时序:

- 1. 复位锁存器置 1, PWRT&OST 清零

- 2. 当内部的 POR、LVR、外部复位或 WDT 溢出复位脉冲加载完成后, PWRT 开始计数

- 3. PWRT 溢出以后, OST 开始计数延迟

- 4. OST 延迟完成以后,复位锁存器清零芯片最后得到的复位信号

#### PWRT(Power-up Reset TIMER): 上电复位计数器

上电复位计数器延迟时间由 SUT[2:0]设置,只要 PWRT 在运行,IC 就一直保持在复位状态。 Vdd、温度和其它变化而会影响 PWRT 控制 IC 的延迟时间。

## 上电复位时间:

| Oscillator Mode | POR/LVR                  | WDT time-out Reset |

|-----------------|--------------------------|--------------------|

| RC              | 18ms /9ms /288 ms /144ms | 140 us             |

#### OST(Oscillator Start-up TIMER): 振荡启动计数器

在上电过程中,PWRT 延迟时间(18/9/288/144ms)之后振荡启动计数器会再提供一个 64 个周期的延迟以使内部 RC8M 时钟稳定,当 OST 计数时,IC 保持为复位状态,直到 OST 计满后复位撤除。另外 RC8M 信号振幅需达到振荡器输入最大振幅后,OST 计数器才开始计数。

# 7. 电气特性

# 7.1 电气特性极限参数

# 表 7 极限参数

| 参数   | 标号               | 条件      | 范围                            | 单位            |

|------|------------------|---------|-------------------------------|---------------|

| 供电电压 | $V_{DD}$         | 1       | -0 to +6.0                    | V             |

| 输入电压 | Vı               | 所有 I/O口 | -0.3 to V <sub>DD</sub> + 0.3 | V             |

| 工作温度 | T <sub>A</sub>   | -       | -40 to + 85                   | ${\mathbb C}$ |

| 储藏温度 | T <sub>STG</sub> | -       | -40 to + 125                  | $^{\circ}$ C  |

# 7.2 直流特性

表 8 如无特殊说明 V<sub>DD</sub> = 2.5V~5.5V, Temp = 25°C

| 参数                            | 标号              | 条件                                                                 | 最小值                  | 典型值 | 最大值                  | 单位   |